### 2024年HIAF高能终端谱仪合作组会议

# 辐射探测前端专用集成电路研究进展

汇报人:郑然\*、王佳、赵瑞光、魏晓敏、薛菲菲、胡永才

zhengran@nwpu.edu.cn

# 报告内容 CONTENTS

- 1 高精度时间检测及量化电路 (NTIMP)

- 2 多通道低噪声直流耦合前端读出芯片

- 3 STCF量能器读出电子学芯片设计

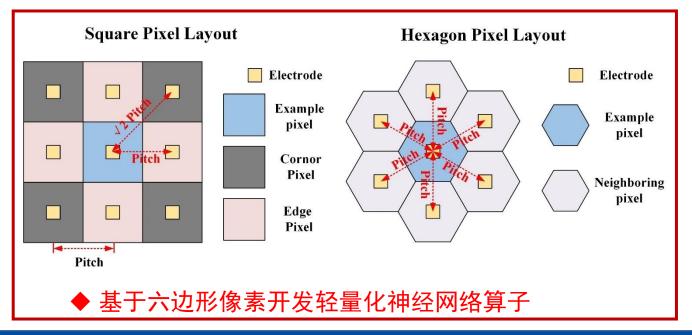

- 4 基于数据驱动的智能压缩读出

5 片上集成神经网络的智能化像素探测器

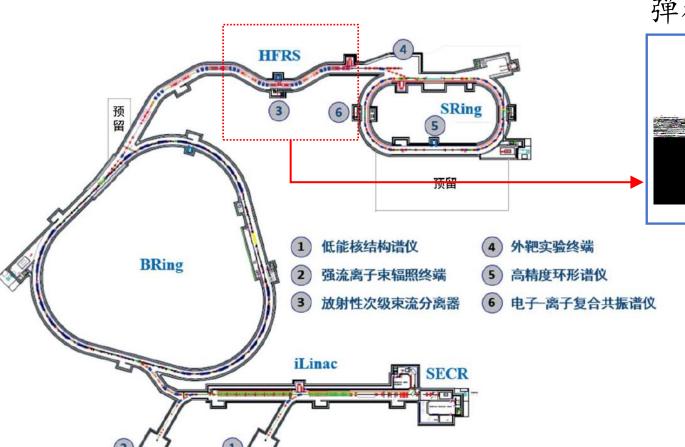

□ 应用背景─强流重离子加速器装置(HIAF)

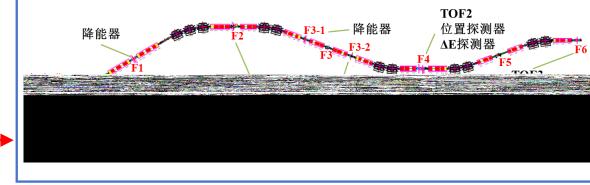

弹核碎裂型次级束流装置 (HFRS)

#### 在HFRS上采用 $B\rho$ -TOF- $\Delta E$ 法实现粒子鉴别:

- ✓ ΔE探测器: 获取粒子的能损信息;

- ✓ 位置探测器: 获取粒子的磁刚度信息;

- ✓ TOF探测器: 获取粒子的飞行时间信息;

要求优于40 ps的时间精度,以鉴 别较重较快的碎片

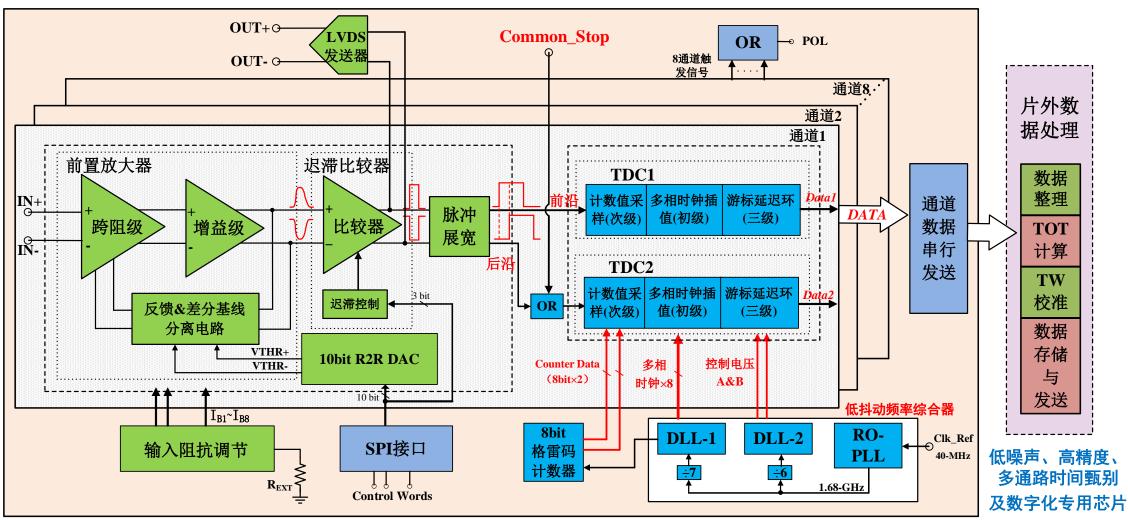

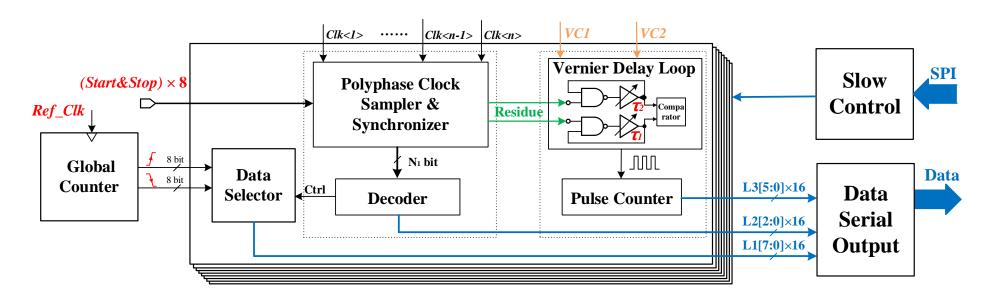

□ NTIMP3 前放甄别电路 + 基于游标延迟环结构的TDC

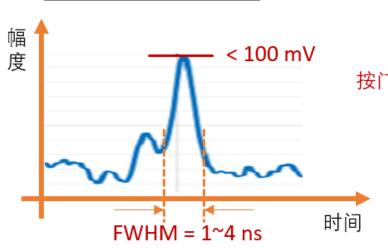

□ 金刚石探测器的信号特征(近物所提供)

#### 金刚石探测器的优势:

- ✓ 高载流子迁移率,适合用于时间探测

- ✓ 抗高温,适合高温环境工作

- ✓ 抗辐射,适合于空间及地面辐射环境

- ✓ 导热率高,适合集成大型探测器系统

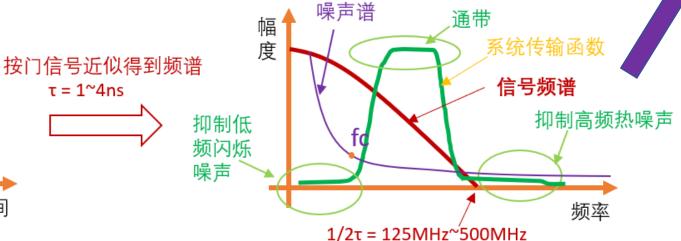

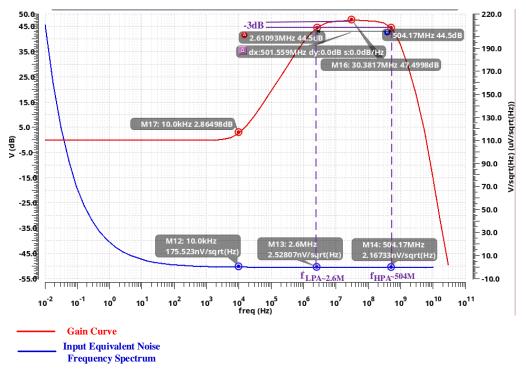

滤波设计: 带通 (2M~500M) 噪声优化对象: 热噪声

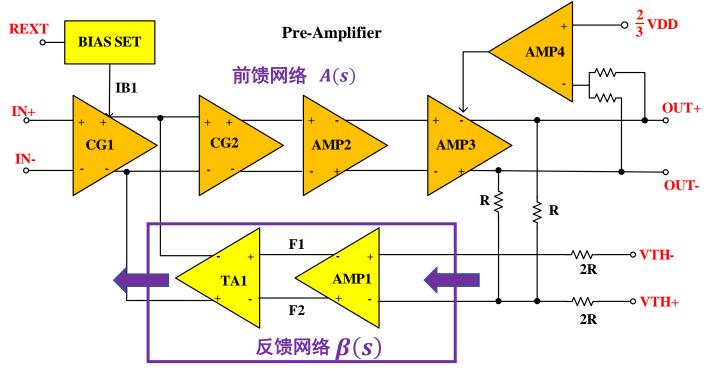

#### □ 前放甄别电路——滤波设计

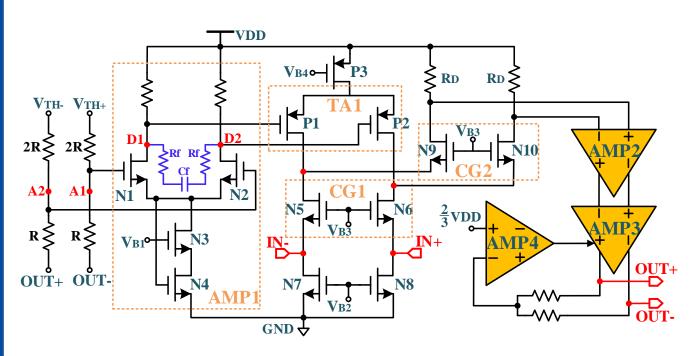

$$H(s) = \frac{A_{CG1}(s)A_{CG2}(s)A_{AMP2}(s)A_{AMP3}(s)}{1 + A_{CG2}(s)A_{AMP2}(s)A_{AMP3}(s)A_{TA1}(s)A_{AMP1}(s)}$$

前馈通路增益远大于1

$$H(s) = \frac{A_{CG1} * (1 - s/P_{AMP1})}{A_{TA1} * A_{AMP1}}$$

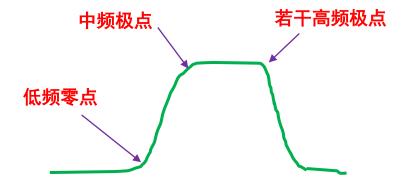

低频零点

AMP1 贡献低频零点、中频极点, AMP2, AMP3贡献高频极点。

#### 简化反馈系统:

$H(s) = \frac{A(s)}{1 + \beta(s)A(s)}$

$\beta(s)$ 幅

令低频 $\beta(s)$ 较大,

$H(s) \approx 1/\beta(s)$  低频阻带

令中高频 $\beta(s)$ 较小, $\beta(s)A(s) \ll 1$

$H(s) \approx A(s)$  中高频通带

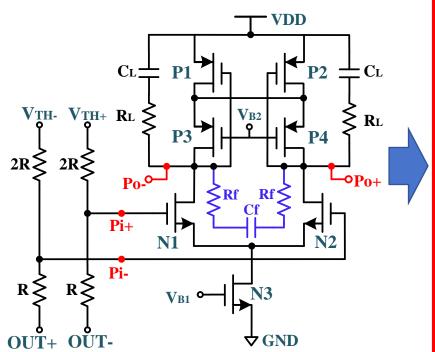

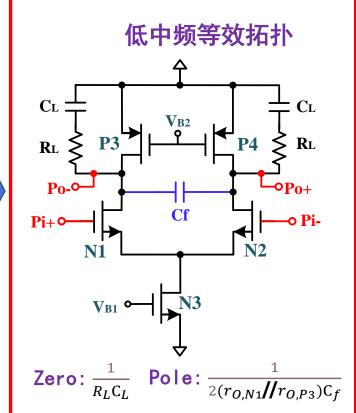

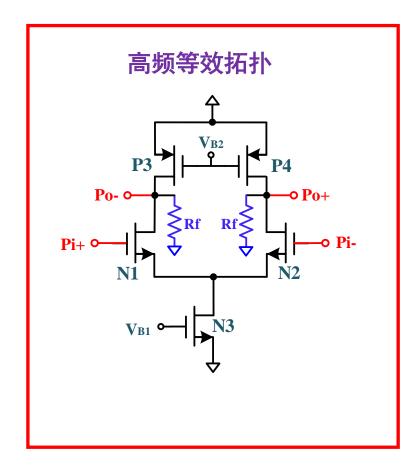

#### $\square$ 前放甄别电路设计—— $\beta(s)$ 的动态拓扑设计

低频增益(20-30)  $A_{V} \approx g_{m,N1}(r_{O,N1}//r_{O,P3})$

高频增益 (小于0.1)  $A_{\rm V} \approx g_{{\rm m},N1}R_f$

□ 前放甄别电路设计——通带仿真

通带: 2.6MHz-504MHz

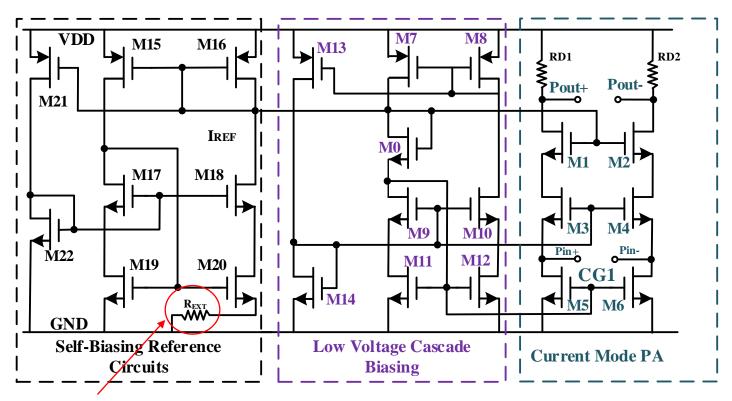

#### □ 前放甄别电路设计——外部可调输入阻抗

#### 外部电阻

$$R_{IN} = \frac{1}{g_{m3}} = \frac{R_{EXT}}{2\sqrt{\frac{M3*M5*M8}{M19*M11*M16}}*(1-\sqrt{\frac{M19}{M20}})}$$

输入阻抗50Ω~250Ω可调

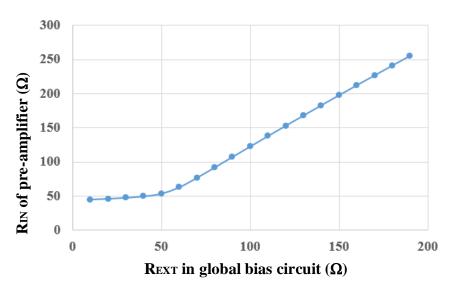

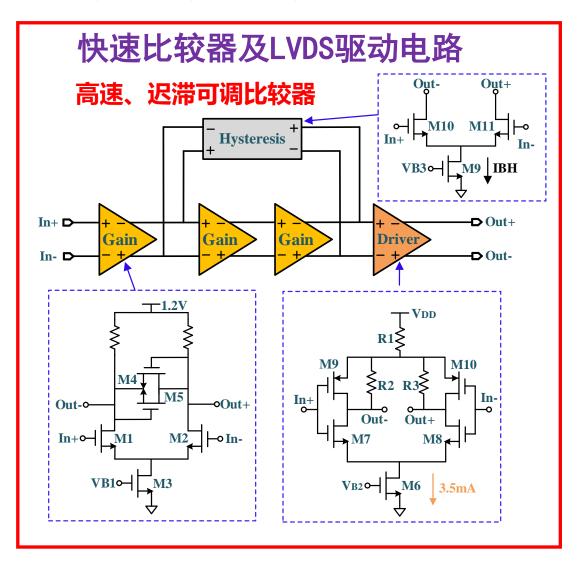

□ 前放甄别电路设计——其他电路

#### □ 基于游标延迟环结构的TDC设计

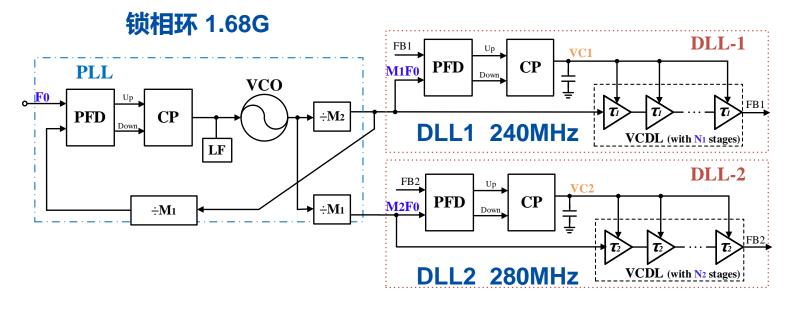

#### □ 基于游标延迟环结构的TDC设计 ─ 频率综合器设计

#### 频率综合器输出时钟抖动

| 时钟      | P2PJitter | RMSJitter | 周期数   |

|---------|-----------|-----------|-------|

| 240MHz  | 10.625Ps  | 1.72Ps    | 1000  |

| 280MHz  | 12.819Ps  | 2.07Ps    | 1000  |

| 1680MHz | 12.048Ps  | 1.62Ps    | 10000 |

#### 频率综合器的实现

锁相环: 高主频, 低抖动

分频器:采用TSPC触发器实现,配合逻辑线路实现50%占空比。

双DLL: 产生VDL延迟单元的控

制电压

VCO: 采用三级基于DCVSL-R结构的延迟单元,产生更加对称震荡波形,减少相位噪声累积。

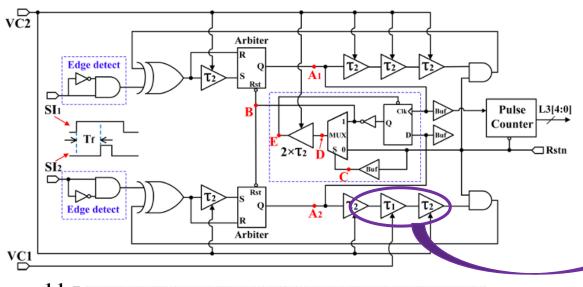

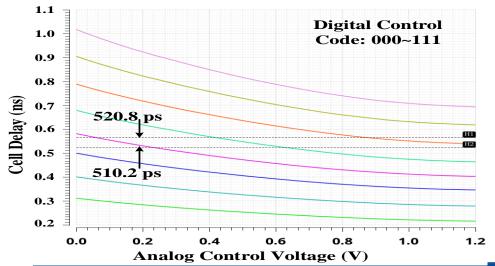

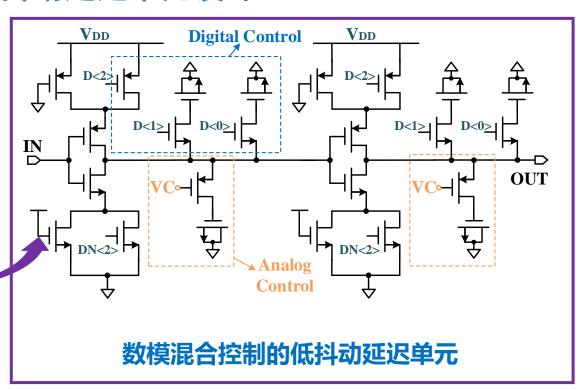

### □ 基于游标延迟环结构的TDC设计 — 低抖动延迟单元设计

- ◆ 降低延迟曲线斜率,减少电压噪声向抖动的转化;

- ▶ 增大延迟调节范围,提高设计兼容性

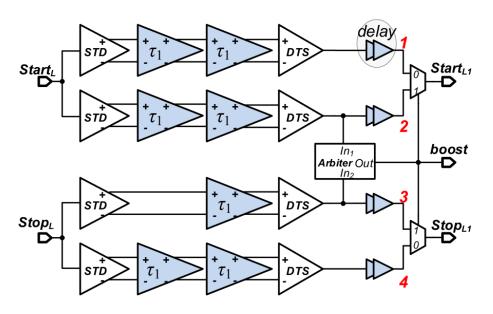

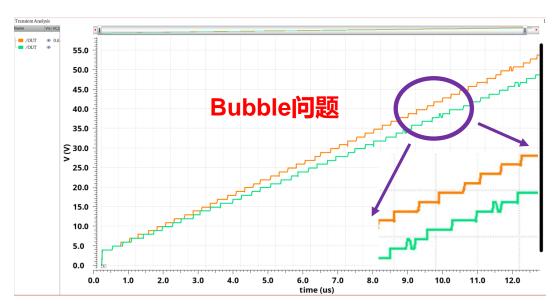

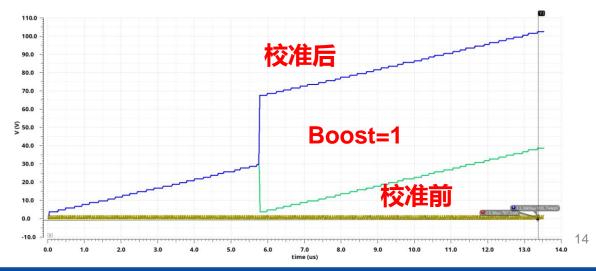

#### □ 基于游标延迟环结构的TDC设计 ─ 游标延迟链校准电路

当待测时间间隔Tin小于Tc(VDL量程)/2时: VDL接收到的时间间隔Tm=Tin;

当Tin>Tc2时: VDL接收到的Tm=Tin-Tc/2。 从而相当于将VDL的最大循环次数减少了一半, 减少了抖动累积,提高了测量精度。

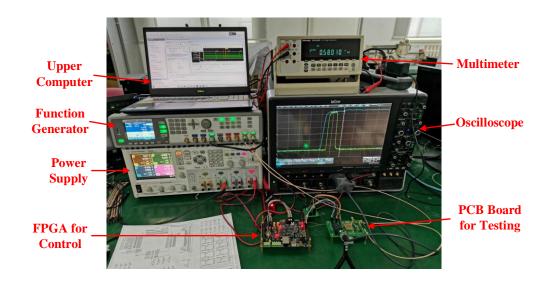

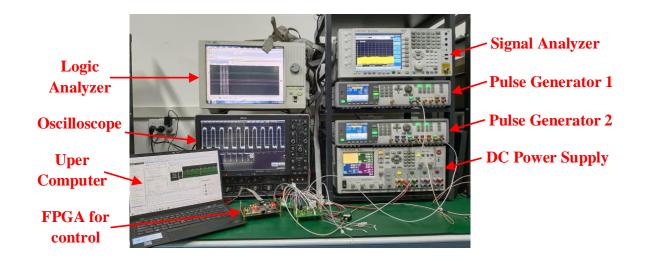

#### 前放甄别电路测试系统

#### TDC测试系统

(鸣谢IMP赵承心老师在技术和流片资源方面的支持) TNS, 2023; NST 2024

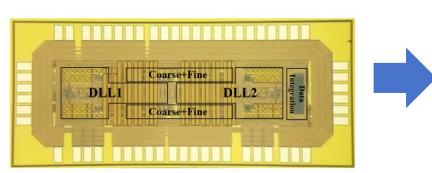

NTIMP1——8通道模拟前端 ASIC,精度15ps(2021~2022)

NTIMP2——8通道模拟前端 ASIC,功能完善(2022~2023)

双通道多级游标型TDC,精度 110ps (2020~2021)

8通道多级游标型TDC,精度46ps (2022~2023)

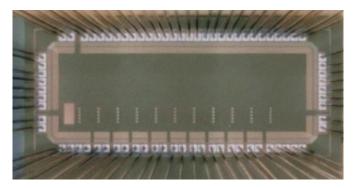

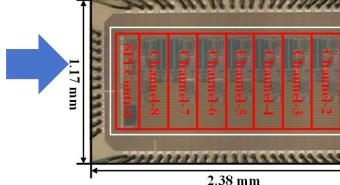

NTIMP3——8通道前端+TDC ASIC, (2024年8月tape out) 23) 15ps +10ps

| 芯片名称     | 设计者     | 应用领域        | 工艺尺寸       | 边沿抖动   | 功耗/通道 | TW修正方式  | 数字化方式 |

|----------|---------|-------------|------------|--------|-------|---------|-------|

| NINO     | CERN    | 多用途         | 250nm      | 25 ps  | 40mW  | TOT离线修正 | 片外TDC |

| PADI     | 德国 CBM  | 多用途         | 180nm      | 20 ps  | 17mW  | TOT离线修正 | 片外TDC |

| FEERIC   | 法国LPC   | ALICE实验     | 350nm      | 400 ps | 60mW  | 过零甄别    | /     |

| FlexToT  | 巴塞罗那大学  | TOF-PET     | 350nm      | 30 ps  | /     | TOT离线修正 | /     |

| FATIC    | 意大利INFN | 微型气体<br>探测器 | 130nm      | 300 ps | 50mW  | /       | 片外TDC |

| ALTIROC  | 法国OMEGA | ATLAS实验     | 130nm      | 30 ps  | 4.5mW | TOT离线修正 | 片内TDC |

| CAD-II   | 清华大学    | 多用途         | 180nm      | 20 ps  | 15mW  | TOT离线修正 | 片外TDC |

| APDROC   | 高能所     | 加速器实验       | 130nm      | 35 ps  | 21mW  | TOT离线修正 | 片外TDC |

| LGADROC  | 中科大     | ATLAS实验     | 130nm      | 20 ps  | 4mW   | TOT离线修正 | 片内TDC |

| NTIMP1,2 | 西北工业大学  | HIAF实验      | 130/180 nm | 15ps   | 14mW  | TOT离线修正 | 片外TDC |

# 报告内容 CONTENTS

- 1 高精度时间检测及量化电路 (NTIMP)

- 2 多通道低噪声直流耦合前端读出芯片

- 3 STCF量能器读出电子学芯片设计

- 4 基于数据驱动的智能压缩读出

5 片上集成神经网络的智能化像素探测器

**18** 18

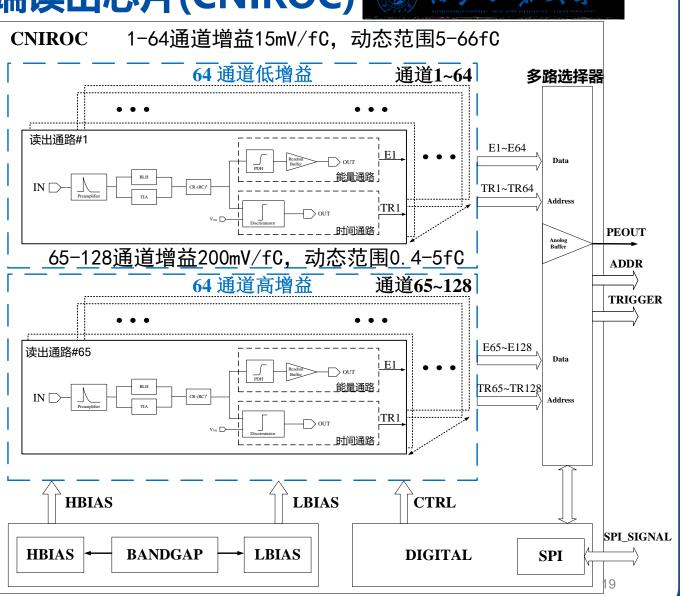

### |多通道、低噪声、直流耦合前端读出芯片(CNIROC)

256像素阵列式碲锌镉探测器

128通道高低增益直流耦合前端读出芯片

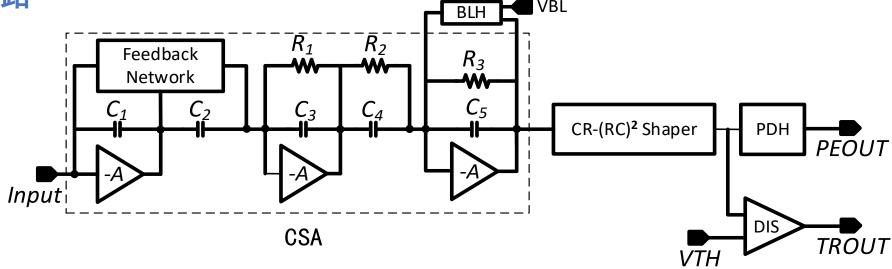

### |多通道、低噪声、直流耦合前端读出芯片(CNIROC) ② ダルスオスタ

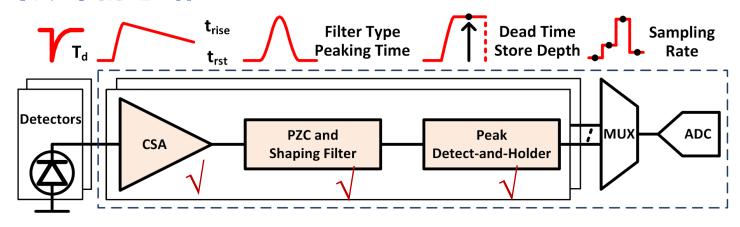

- ◆ 三级前端放大器;

- ◆ 探测器泄露电流补偿, 范围10pA-5nA;

- ◆ 两级成形器, 0.5us-2us可调;

- ◆ 峰值保持电路,由数字电路控制复位;

- ◆ 事件甄别电路,提供触发信号

- ◆ 电容比例放大增益更精确;

- ◆ 三级电路共同构成C-V放大器, 第三 级实现复位时间与事例率的折衷。

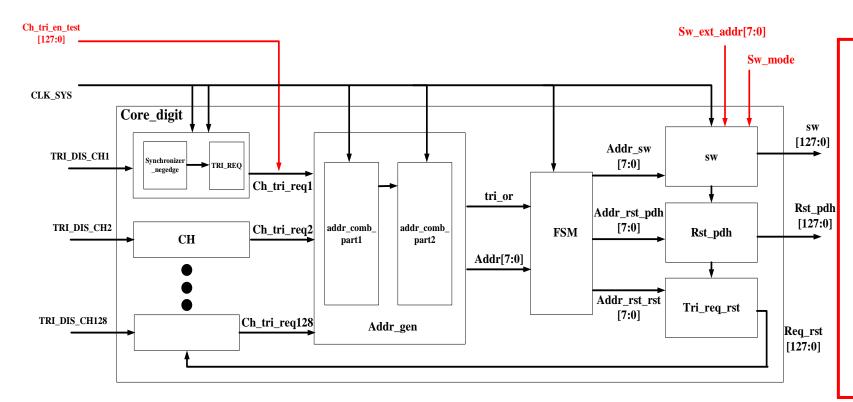

### |多通道、低噪声、直流耦合前端读出芯片(CNIROC)

#### □ 片内数字控制电路

#### ◆ 工作模式:

128通道正常开启并监测 事件, 当事件到来时输出相 应通道能量信号、TRI信号及 地址信号等,并进行复位等 操作:

#### ◆ 测试模式:

可指定某通道持续观察其 输出,可用于测试、排错。

- ◆ 控制通道输出选通、通道复位、地址编码、成形时间调节等功能。

- ◆ 通过SPI配置寄存器关闭特定通道触发功能,测试或屏蔽异常通道。

### |多通道、低噪声、直流耦合前端读出芯片(CNIROC)

北京大学200Krad辐照实验

| <del>1</del> 5 <b>:</b> = | 高增益      | @2us     | 低增益@2us   |           |  |

|---------------------------|----------|----------|-----------|-----------|--|

| 指标                        | 辐照前      | 辐照后      | 辐照前       | 辐照后       |  |

| 增益                        | 172mV/fC | 166mV/fC | 18.1mV/fC | 18.2mV/fC |  |

| ENC                       | 83.7e-   | 93.5e-   | 172.6e-   | 180.3e-   |  |

| 线性范围                      | 0.7-7fC  | 0.7-7fC  | 4-66fC    | 4-66fC    |  |

| 非线性度                      | 1.24%    | 1.7%     | 1.12%     | 1.18%     |  |

## 报告内容 CONTENTS

- 1 高精度时间检测及量化电路 (NTIMP)

- 2 多通道低噪声直流耦合前端读出芯片

- 3 STCF量能器读出电子学芯片设计

- 4 基于数据驱动的智能压缩读出

5 片上集成神经网络的智能化像素探测器

**23**

### ISTCF量能器读出电子学芯片设计

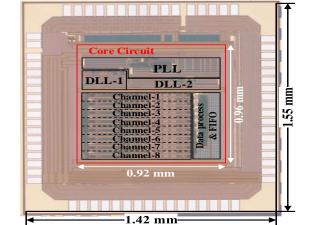

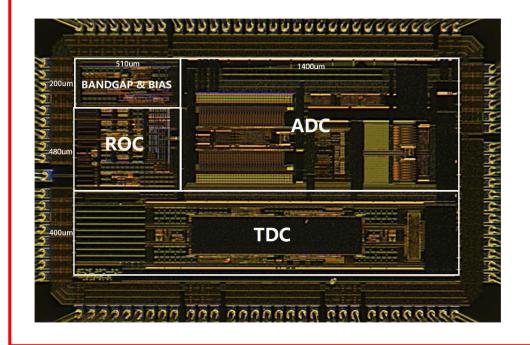

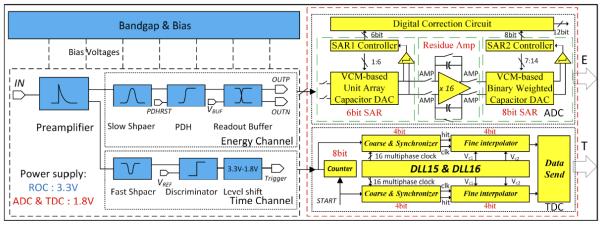

**SECALROC1/2** NIM,2021 TNS, 2023

设计了一款低噪声、高速率全数字输出混合

信号前端读出ASIC。该ASIC包含模拟前端读出电路、ADC和TDC,可完成对输入信号幅度以及到达时间的精确测量。

Fig. 1. Diagram of the proposed ASIC for both energy and time measurement. This ASIC is composed of an analog ROC, a built-in bandgap and bias circuit, a two-stage pipelined SAR ADC, and a 16-bit three-stage TDC (counter + coarse interpolators + vernier delay loop fine interpolators). A 3.3-V power supply is applied for the ROC, and a 1.8-V power supply is employed in the ADC and TDC.

#### TABLE III SECALROC2 ASIC FEATURES

| Technology                     |                 | 0.18-μm Mixed-Signal CMOS                                                |  |  |

|--------------------------------|-----------------|--------------------------------------------------------------------------|--|--|

| Input charge (Particle energy) |                 | $3.2 \text{ fC} \sim 400 \text{ fC}$<br>(20 MeV $\sim 2.5 \text{ GeV}$ ) |  |  |

| Shaping filter type            |                 | CR-RC <sup>5</sup>                                                       |  |  |

| Peaking time                   |                 | 200, 275, 350, 425, 500, 800 ns                                          |  |  |

|                                | Nonlinear error | < 2.5%                                                                   |  |  |

|                                | ENC without APD | $1367e^- + 4.93e^-/pF$<br>@ $T_p = 800 \text{ ns}$                       |  |  |

|                                | ENC with APD    | $3820e^{-}$<br>@ T <sub>=</sub> = 425 ps. $L_{z}$ = 13.5 pA              |  |  |

|                                | Time resolution | < 540 ps<br>@ OIN>160 fC, VTH = 0.3 V                                    |  |  |

| Power supply voltages          |                 | 3.3 V (ROC)<br>1.8 V (ADC & TDC)                                         |  |  |

| Power consumption              |                 | 35 mW (ROC)<br>20 mW (ADC) + 15 mW (TDE)                                 |  |  |

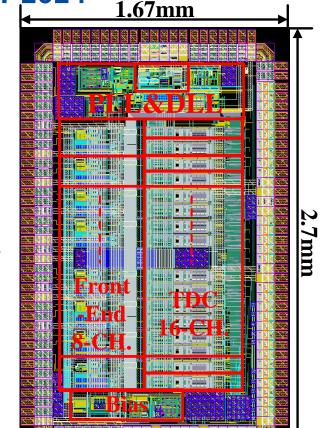

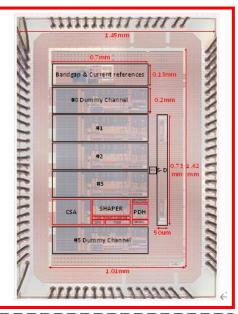

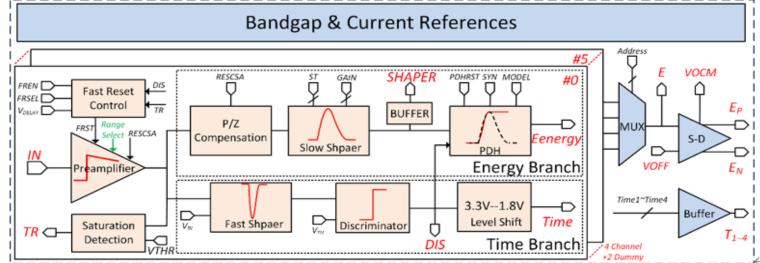

### **ISTCF**量能器读出电子学芯片设计

#### SECALROC3 NST, 2024

在STCF ECAL中,由于辐射本底事件影响,对ASIC提出了更高计数率需求,因此在SECALROC1芯片基础上,增加电荷灵敏放大器快速复位电路,并优化峰值采样保持电路,增加前端读出ASIC的事件处理速度。

#### 1、关键指标←

4 Channel (+2 Dummy channel) ←

Noise:←

ENC<5000e @ Cin = 289pF←

ENC<1875e @ Cin = 0pF

ENC Slope: ←

9.1e-/pF @ PT = 60ns ←

3.33e-/pF @ PT = 1.68us←

Time resolution: ←

174ps @QIN=160fC, VTH=0.9V (FSH+DIS) ←

80.1ps @QIN=160fC, VTHR=0.9V (CSA+DIS) <

Gain:←

2.7mV/fC @ DR = 500fC←

10mV/fC @ DR = 100fC←

Maximum charge detectable per event: 500fC←

Nonlinearity: <3₩

Peaking time: 60ns~1.68us←

Maximum count rate: 4MHz<sup>←</sup>

Power dissipation: 35mW/ch<sup>←</sup>

### **ISTCF**量能器读出电子学芯片设计

#### 量能器芯片提高计数率的思路

#### 信号堆叠节点

- CSA输出信号节点电压可堆叠,但一直堆 叠会导致输出电压满摆幅,无法接受新的 事件。

- 成形器输出信号堆叠,造成信号的峰值信息出现误差或信号消失。

- 峰值采样电路存在死区时间,降低了模拟前端读出电路的信号处理速度。

#### 优化设计技术

- 为CSA添加满量程检测以及快速复位模块,当检测到CSA输出满摆幅后,对 CSA进行快速复位,实现利用CSA可堆叠特性的同时,增加CSA的计数率。

- 设计高阶成形滤波器,利用其信号一定程度可堆叠的能力,以及提供堆叠误 差幅度(用于后期误差校准算法),减小输入信号之间的时间间隔限制,提 高系统计数率。

- 增加PDH电路的存储深度,形成两存储单元的循环工作;此外将PDH复位时间隐藏在成形器达峰时间之内,消除死区时间。

# 报告内容 CONTENTS

- 1 高精度时间检测及量化电路 (NTIMP)

- 2 多通道低噪声直流耦合前端读出芯片

- 3 STCF量能器读出电子学芯片设计

- 4 基于数据驱动的智能压缩读出

5 片上集成神经网络的智能化像素探测器

**27** 27

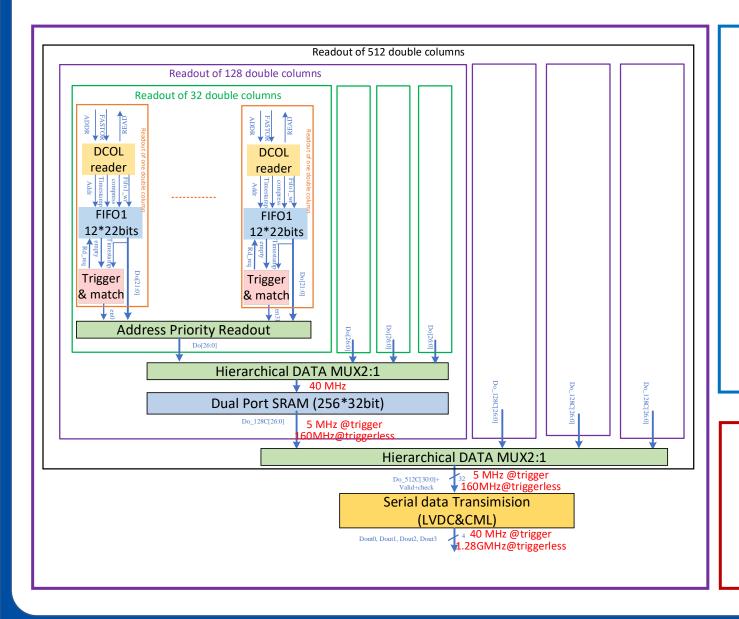

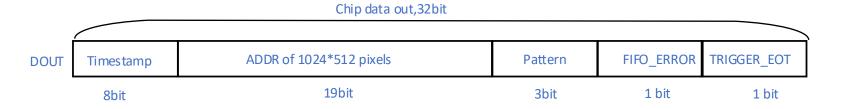

### |基于数据驱动的智能压缩读出

应用背景: CEPC MOST2 关键设计:

- ◆ 阵列 1024×512 数据率120MHz

- ◆ 兼容ALPIDE和FEI3的数据驱动读出时序

- ◆ 支持trigger和triggerless两种工作模式

- ◆ 两级FIFO: 暂存数据, 匹配接口

- ◆ 层次化读出设计:底层采用地址优先的读出方式;顶层采用令牌控制读出,避免数据拥塞

- ◆ 支持临近地址实时压缩

#### 技术优势:

- ◆ 提高电路处理高数据率数据的能力

- ◆ 减小所需两级FIFO的存储深度

- ◆ 减少所需输出的数据量

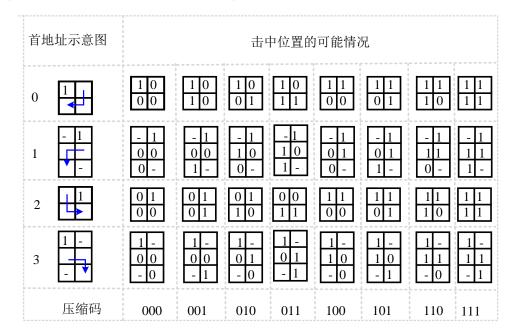

### |基于数据驱动的智能压缩读出

0 <u>1</u> 3 2

首地址情况

0 没击中

□ 不关心

1 击中

簇团搜索方向

### 临近地址压缩

临近的地址压缩成一个数据包,仅记录首地址,压缩范围内其他地址用0/1表示。

图中显示了邻近四个地址压缩的情况 及压缩码

#### 定义输出数据格式:

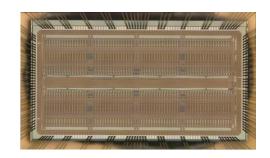

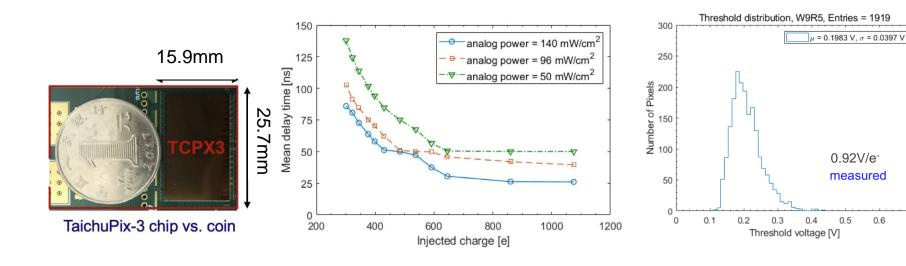

### 芯片测试

- 芯片尺寸: 15.9mmx25.7mm

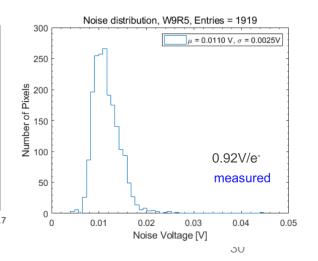

- 像素阈值和噪声:

- Threshold: ~215e-

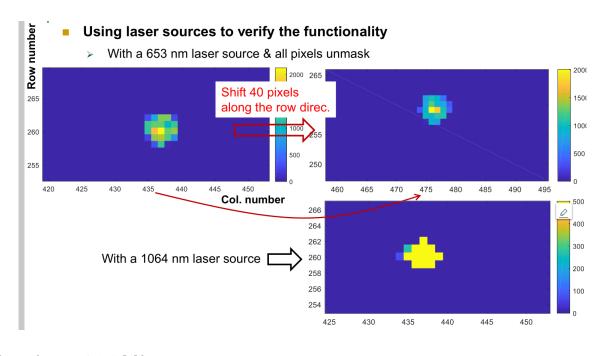

- Noise: FPN 43e<sup>-</sup>, random ~12e<sup>-</sup>

- 激光测试: Sensor+ pixel analog + pixel digital

- + periphery readout + data interface 功能正常

- 响应速度测试: APULSE输入, 统计输出的Timestamp

- Time walk: ~60-95ns

- 功耗: 89-164 mW/cm² (不同Bias) @ Clk: 40 MHz & Serdes: 160Mbps

0.92V/e-

measured

0.6

# 报告内容 CONTENTS

- 1 高精度时间检测及量化电路 (NTIMP)

- 2 多通道低噪声直流耦合前端读出芯片

- 3 STCF量能器读出电子学芯片设计

- 4 基于数据驱动的智能压缩读出

**31** 31

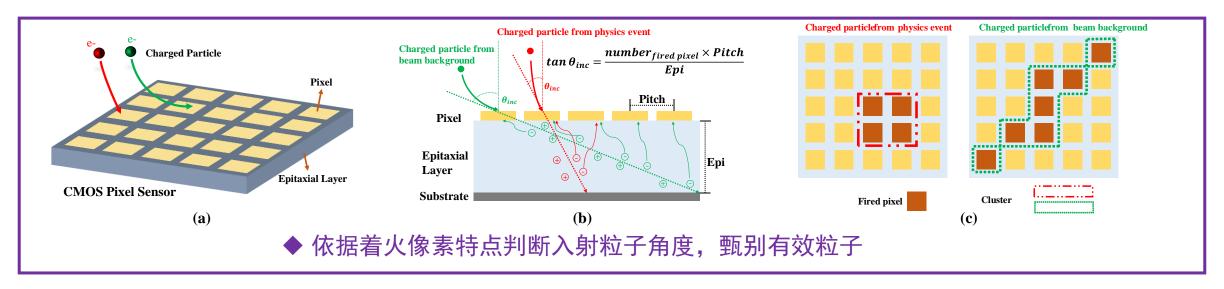

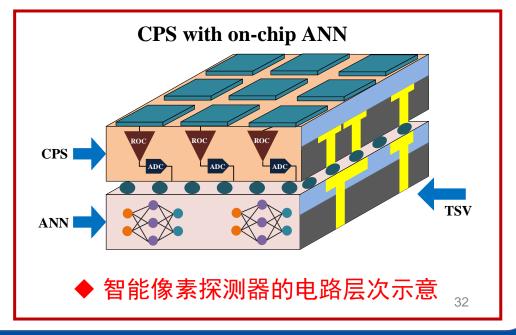

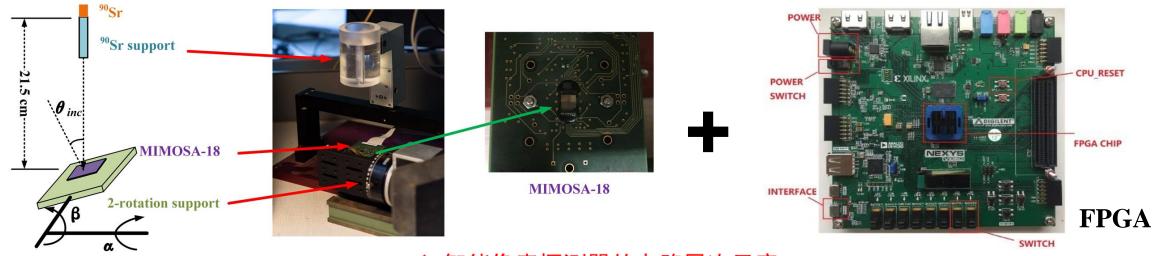

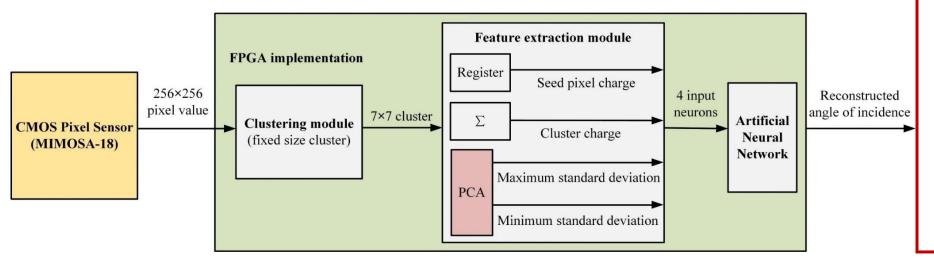

### I片上集成神经网络的智能化像素探测器

### I片上集成神经网络的智能化像素探测器

◆ 智能像素探测器的电路层次示意

- ◆ 入射粒子80%以上 为背景粒子。

- ◆ 该技术可筛除90% 以上的背景粒子, 大大减小数据处 理和传输的压力

### |西北工业大学微电子学研究所——团队负责人

胡永才,博士,西北工业大学特聘教授/博导;

第五批国家"千人计划"专家;

欧洲核子中心科学技术委员会常务委员会的委员;

法国国家研究协会高速图像及光学分会的常务会员;

加拿大/美国国家自然与技术科学基金的评委委员;

多个IEEE集成电路顶级会刊编委及审稿,诺贝尔奖候选者推荐人。

主要研究领域包括:集成电路辐射加固设计技术;集成电路低噪声设计技术;空间应用的CMOS光学传感器、大型核物理实验仪器读出专用集成电路等。

### **|西北工业大学微电子学研究所介绍—团队成员**

郑 然 副教授/博士/博导

2013年获西北工业大学博士学位。比利时鲁汶大学及美国德州大学奥斯汀分校访问学者。

主要研究方向: 图像传感器辐射效应; 辐射探测前端电子学; 快速时间沿检测 技术; 高精度时间数字转换电路。

### ② 西北工業大學

王 佳 副教授/博士/硕导

2013年同时获得法国斯特拉斯堡大学、西 北工业大学博士学位。比利时鲁汶大学访 问学者。

主要研究方向:辐射探测前端电子学设计; 多通道前端电路设计;片上电源芯片设计; 抗辐射电源设计。

### |西北工业大学微电子学研究所介绍—团队成员

魏晓敏 副研究员/博士/硕导

2013年获法国斯特拉斯堡大学博士学位。

主要研究方向: SRAM的抗辐射设计技术、MAPS顶点探测器数据传输及时序控制电路设计技术,混合像素型探测器集成技术。

薛菲菲 副研究员/博士/硕导

2018年获西北工业大学计算机科学与技术博士学位。

主要研究方向: 抗辐射高精度模拟-数字转换电路设计技术; 抗辐射高精度时间-数字转换电路设计技术。

赵瑞光 助理教授/博士/硕导

2020年获法国斯特拉斯堡大学博士学位。

主要研究方:未来加速器 背景粒子筛查及海量数据 处理技术;智能探测器读 出芯片设计技术。

### |西北工业大学微电子学研究所介绍—承担课题

- ▶ 国家重大科学仪器专项/重点研发计划

- 1. 碲锌镉探测器前端读出专用集成电路芯片开发 (课题 2012-2016)

- 2. 三维探测器电子学读出与抗辐射性能研究 (课题 2023-2026)

- 3. 用于对撞机实验和其它应用的单片有源硅像素探测器(合作 2024-2027)

#### ▶ 国家自然科学基金重点(专项)项目

- 1. 面向粒子辐射探测领域应用的具有高通用性、超多通路全数字输出前端读出芯片关键技术研究(主持 2019-2023)

- 2. X射线成像和能谱分析的多通道硅漂移探测器阵列研究(合作 2019-2023)

- 3. 新一代2-7GeV能区超高亮度正负电子对撞机硅像素内径迹探测器关键技术研究(合作2024-2027)

#### > 国家自然科学基金其他项目

- 1. 空间辐射下CMOS图像传感器RTS噪声研究 (2012-2015)

- 2. 抗辐射单片有源像素粒子探测器关键技术研究(2016-2019)

- 3. 空间环境下CIS暗电流幅值分布模型研究 (2014-2016)

- 4. 片上异构复杂电源集群拓扑结构及构建算法研究 (2016-2018)

- 5. 大阵列高速MAPs的采样策略及电路结构研究 (2018-2020)

- 6. 面向粒子辐射探测领域应用的抗辐射低功耗ADC关键技术研究(2022-2024)

- 7. 在辐射探测领域智能化CMOS像素探测器中应用的人工神经网络的关键技术研究 (2023-2026)

- 8. 面向CMOS像素探测器片上集成的cluster实时找寻算法和电路结构研究 (2023-2025)

- 9. 应用于辐射探测的低噪声、高精度、多通路时间甄别及数字化专用集成电路设计方法研究(2024-2027)

- 10. 大面阵CdZnTe探测器宽能区射线作用深度测量ASIC研究 (2025-2028)

### l西北工业大学微电子学研究所介绍

- ▶ 工信部2023产业基础再造和制造业高质量发展专项

- 1、2023年核辐射便携式监测仪 (2023-2026)

#### > 其他重要课题

- 1. 国家重点研发计划大科学装置前沿研究重点专项,高能正负电子对撞机 (CEPC) 关键技术的研发和验证 (2018-2023)

- 2. 中国科技大学陶粲粒子工厂 (STCF) 加速器预研—量能器专用ASIC研发 (2019-2023)

- 3. 兰州重离子加速器放射性次级束流装置的弹核碎片分离设施(HFRS)TOF检测芯片研发(2020~2024)

- 4. 基于反应深度修正的高精度能谱专用读出电子学芯片研发(迪泰克)(2022-2025)

- 5. 辐射探测器128通道前端电子学读出芯片研发(中核西仪) (2022-2026)

# Thanks

汇报人: 郑然